## 巨大データ流通を支える次世代光ネットワーク技術 の研究開発

平成30年10月10日

代表研究機関·研究者 日本電信電話株式会社 富澤 将人

共同研究機関

三菱電機株式会社日本電気株式会社富士通株式会社

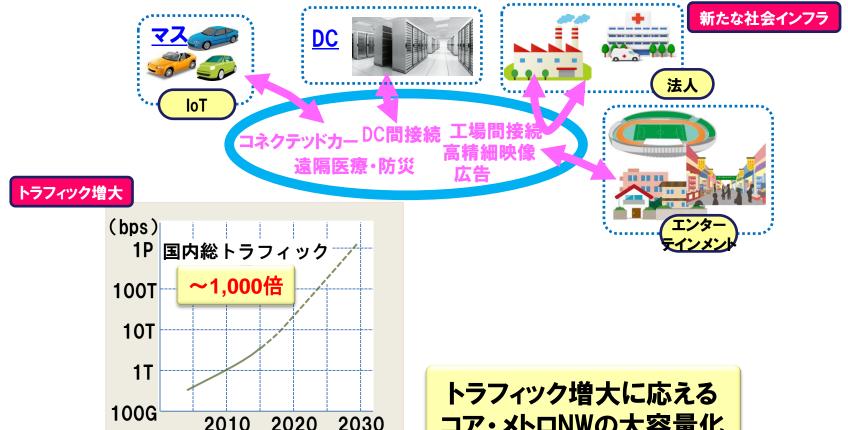

# 取り巻く環境の変化

- ・2020年東京オリンピックから10年後となる2030年の時代には、コネクテッドカー等のIoT技術の多く が確立・成熟期を迎え、AI/IoTを活用したサービスの重要性が増し、新たな社会インフラへ変化

- ・それに伴い、通信ネットワークの観点からは、トラフィックの増大が想定。2030年のトラフィック量は 2010年比で数百倍から1000倍規模に増大

2004~2015年は総務省「我が国のインターネットに おけるトラヒックの集計結果」2016以降はCAGR40% を仮定した予測。

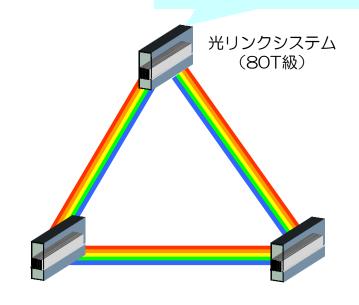

コア・メトロNWの大容量化

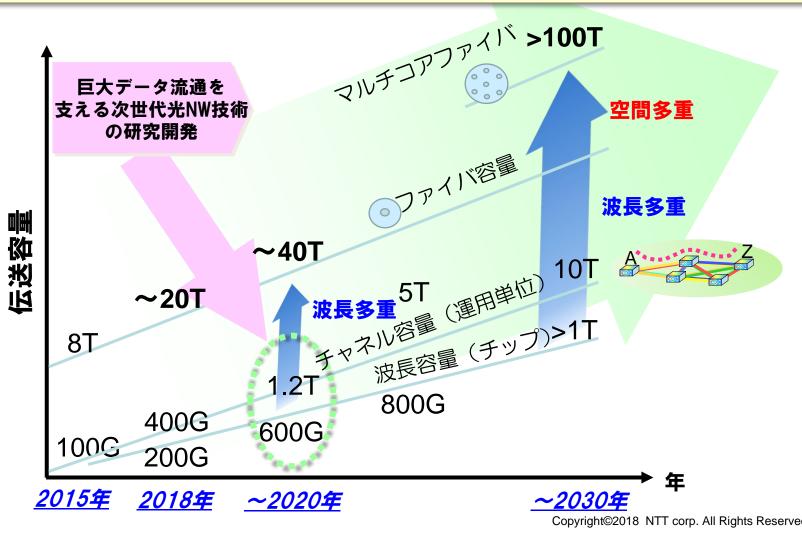

# 本研究の位置づけ

さらなる高速大容量化と低消費電力化を進めた光伝送技術が要求されており、 1T級の光伝送技術の先行確立が必須

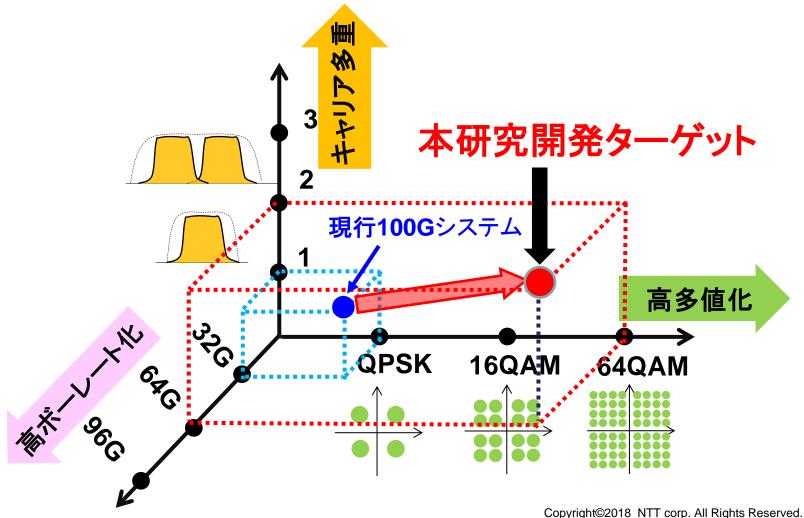

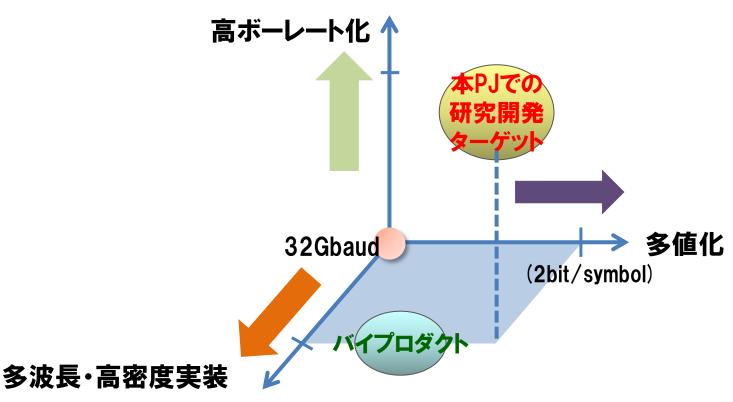

# 大容量化の方向性

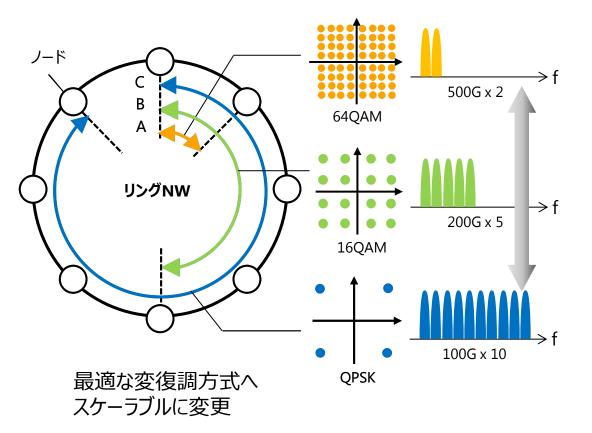

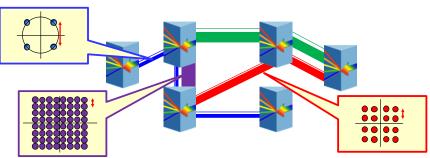

### 高ボーレート化、高多値化、マルチキャリア多重化により大容量伝送を実現

## テラビット級ネットワーク実現における実装サイズのインパクト

従来100G技術における実現イメージ

所要スペース:10

消費電力:10

(従来100Gを1とした場合)

本技術開発における実現イメージ

1/10の省スペース化 消費電力1/4

所要スペース:1

消費電力: 2.5

(従来100Gを1とした場合)

# 課題 I-ア-(a) 適応変復調基本技術

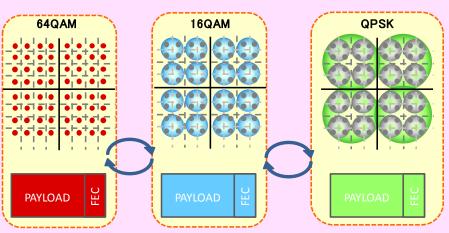

### 伝送路特性推定による適応的な変復調方式の選択により1 Tbps級光伝送を実現

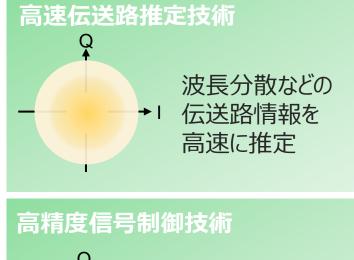

- ・ 高度な変調方式に対応した伝送路特性推定技術の確立

- ・ 伝送路特性に対して1Tbit/s級光信号を適応的に構成する変復調制御技術

- ・ 各種多値信号の信号点配置を最適化する高精度信号制御技術の検討

送信デバイスの

波形歪みなどを

高精度に制御

# 課題 I-ア-(b) 誤り訂正基本技術

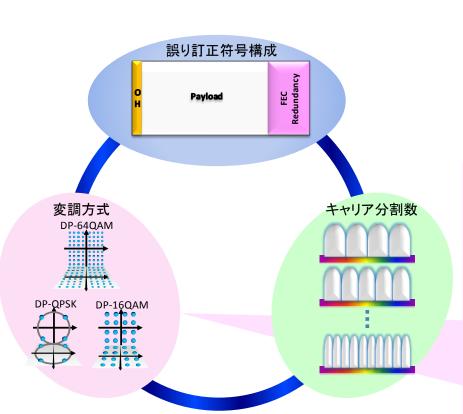

最大1Tbps級の光伝送において、より小さいキャリア分割数や64QAM等の高い多値度にも対応可能な誤り訂正基本技術を確立し、送受信機当たり従来の10倍の伝送容量を実現

- ① 様々なキャリア分割数や多値度に柔軟に対応可能でOTNフレームとの親和性のある 誤り訂正符号化・復号処理アルゴリズム

- ② 様々な多値度に対して対応可能な尤度生成アルゴリズムおよび閾値制御技術

多値度可変、閾値可変による適応変調符号化誤り訂正

# 課題 I -イ-(a) 静的等化基本技術

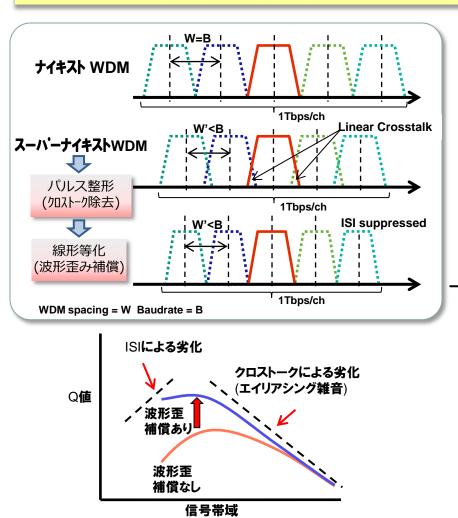

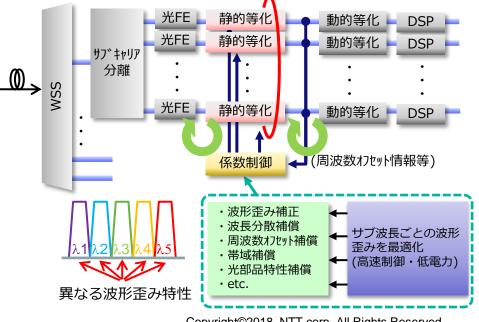

スペクトル整形技術と波形等化技術の組み合わせにより、周波数利用効率を向上 しながら1Tbps級の光伝送を実現する静的等化基本技術を確立する

- 周波数利用効率向上を目指したスペクトル 整形・波形歪み補償技術を確立

- 64QAM等やキャリア分割数変化に対応-

- ② サブ波長ごとの波形歪みを最適化して実装を 考慮した1Tbps級送受信技術を確立

# 課題 I -イ-(b) 動的等化基本技術

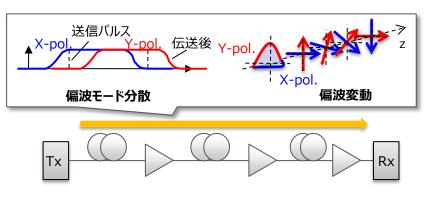

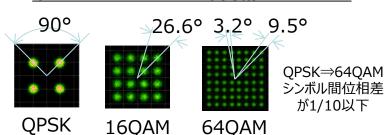

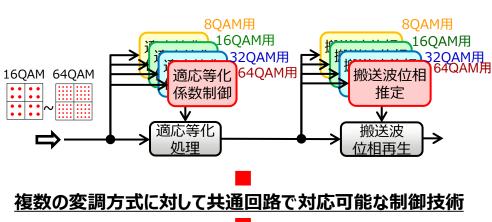

最大64値を視野に入れた変調多値度に対応した上で、偏波変動と偏波モード分散により動的に生じる波形歪みの補正を最も少ない演算規模で実現する信号処理技術の確立

- ① 最大64値の変調多値度に対応した適応等化/搬送波位相再生アルゴリズム

- ② 様々な多値度に対して、高精度・高速な動的等化を低演算規模で実現

#### 伝送波形歪みの動的変動に対する高い追従性

#### 最大64値に対応可能な高精度動的等化

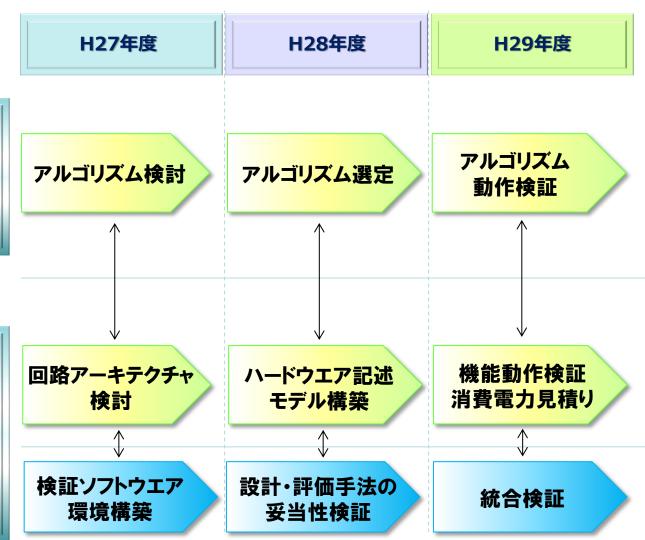

## 研究開発スケジュール

#### 課題 I 1テラビット級高速大容量 光伝送技術

- ア)適応変調符号化技術

- (a)適応変復調基本技術

- (b)誤り訂正基本技術

- イ)伝送システム内歪み補償技術

- (a)静的等化基本技術

- (b)動的等化基本技術

#### 課題 II 1テラビット級低消費電力 光伝送技術

- ア) 信号処理回路最適設計技術

- (a)適応変復調回路基本技術

- (b)誤り訂正回路基本技術

- (c)静的等化回路基本技術

- (d)動的等化回路基本技術

- イ)低消費電力信号処理統合検証 技術

# 研究開発成果1:各技術の確立

· 高速伝送路推定技術、高精度信号制御技術

同期歪み耐力、波長分散・周波数オフセット推定性能並びに変調器などの 送信器アナログ不完全性補償効果を確認

・誤り訂正基本技術

符号化・復号処理・尤度生成アルゴリズム基本機能に対して妥当性を確認

・ 静的等化基本技術

提案したスーパーナイキスト方式による機能モデルを作成し、オフライン実験 による評価を行い、周波数利用効率向上の効果を確認

· 動的等化基本技術

提案した共通回路方式による適応等化/搬送波位相再生アルゴリズムの シミュレーション評価を行い、方式検討および機能モデル作成を完了

· <u>低消費電力信号処理統合検証技術</u>

統合回路の動作データを用いたチップレベルの消費電力評価を実施し、100Gbps あたりの見積り消費電力を第1世代100G-DSPに比較して1/4以下に実現

# 研究開発成果2:回路試作

### 【内容】

チップ実現に向けて、キーとなるDAC/ADCの高ボーレート(65GBaud級)動作に対して実際のDSPロジック回路を部分的に実装し、性能評価を実施

### 【結果】

主要モードの信号疎通を確認し、64Gbaudの様々な変調フォーマットでの動作を実証

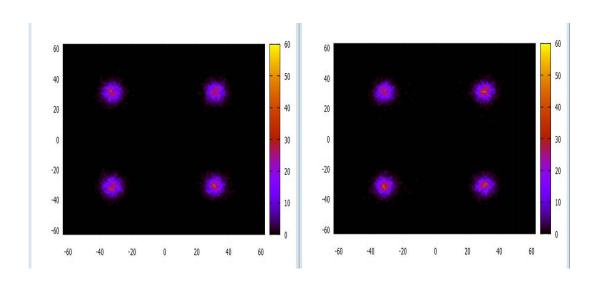

200G QPSKコンスタレーション

# 研究開発成果3:テストチップ試作

- ・ 市場動向調査から低電力DSPの需要を捉え、16nmプロセス のテストチップを試作

- ・ ADC/DAC設計等の本施策成果の一部を取り入れたバイプロ ダクト(超低電力400G対応DSP)化を行い、市場へ投入

# 研究開発成果の社会展開(NTTコミュニケーションズ)

2017年4月7日

NTT コミュニケーションズ株式会社 日本電信電話株式会社

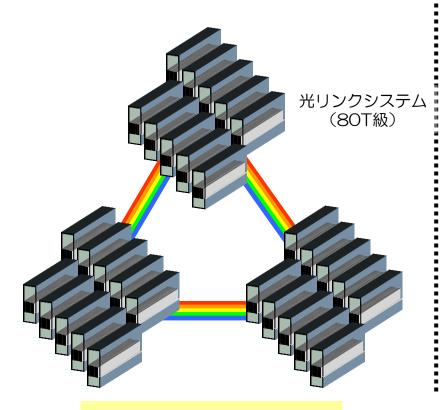

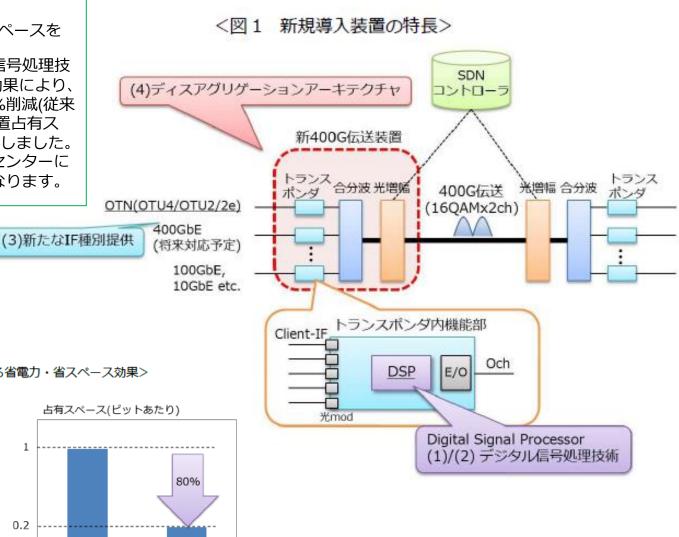

#### データセンター間を接続するネットワークへ 超大容量 400 ギガビット伝送装置を導入

NTT コミュニケーションズ株式会社(本社;東京都千代田区、代表取締役社長:庄司 哲也、以下 NTT Com)は、グローバル展開しているデータセンターの間を接続するネットワークに、大容量伝送かつ省スペース、省電力な 400G 伝送装置を、2017 年 4 月 14 日より順次導入します。

これにより NTT Com の基幹網は、従来の 2 倍以上となる 19Tbps 以上の伝送容量を 1 光ファイバあたりで確保できることとなります。 NTT Com は、IoT の本格的普及などに伴い増加し続けるトラフィックの流通に対して柔軟・迅速に対応する ICT 基盤を引き続き提供して参ります。

なお、本装置に用いられている 400G 伝送技術は、日本電信電話株式会社(本社:東京都千代田区、代表取締役社長: 鵜浦 博夫、以下 NTT)の研究成果であるデジタル信号処理技術を活用したものです。

# 研究開発成果の社会展開(NTTコミュニケーションズ)

#### **2. 本装置の主な特長**(図1)

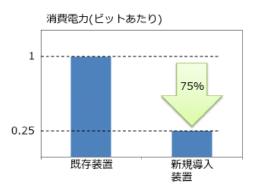

(1)世界最高水準の省電力・省スペースを 実現 (図2)

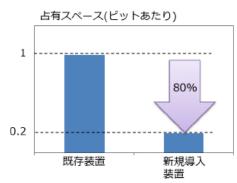

NTTの研究成果であるデジタル信号処理技 術と16nm CMOS技術※2の相乗効果により、 ビットあたりの消費電力を約75%削減(従来 装置比)、またビットあたりの装置占有ス ペースを約80%削減(従来装置比)しました。 面積などにゆとりのないデータセンターに も迅速なサービス提供が可能となります。

<図2 新規導入装置による省電力・省スペース効果>

背景 〉全体概要 〉 研究内容 〉 社会実装 〉 まとめ

## まとめ

- ■本研究開発では1チャネルあたり1Tbps級の容量を有する将来の超大容量光伝送システムを実現するために以下の目標を設定し、他の機能との連携を考慮した機能検証・回路設計検証・消費電力評価を実施した

- (1)64QAMなどのより高度な伝送方式に対応した、 適応変復調技術、誤り訂正技術、静的等化技術、動的等化技術 の基本アルゴリズムを確立

- (2) デジタル信号処理回路の消費電力を従来比1/4(同一通信処理速度で比較)に低減可能で送受信機当たりの伝送容量を従来比10倍(100Gbps級技術と比較)に増大可能な低消費電力化回路構成技術および統合検証技術を確立

- ■大幅な低消費電力化を実現した16nmテストチップを基に商用化完了 各社にて同チップを搭載したシステム導入を実現

- ■一部機能を実装した回路試作を実施し、DAC/ADCの様々な変調方式で 65GBaud級高ボーレートでの動作を確認