## 単一磁束量子デバイスによるニューロチップの開発(052102001)

Development of neurochip using single flux-quantum devices

## 研究代表者

### 小野美 武 東北大学電気通信研究所

Takeshi Onomi, Research Institute of Electrical Communication, Tohoku University

## 研究分担者 金城光永<sup>†</sup>

Mitsunaga Kinjo<sup>†</sup>

<sup>†</sup>東北大学電気通信研究所

<sup>†</sup>Research Institute of Electrical Communication, Tohoku University

研究期間 平成 17 年度~平成 19 年度

### 本研究開発の概要

超伝導体の単一磁束量子を情報担体とする回路を用いて、 $100 \mathrm{GHz}$ の動作周波数を目指したニューロチップの開発を行う。回路速度向上を目的として、ジョセフソン接合のサイズが  $1\mu$  m 角以下の高臨界電流密度 Nb/AlOx/Nb 接合集積化によるスイッチング速度の高速化、マイクロストリップラインを用いた磁束量子信号の高速伝送、さらに多層配線化による 3 次元的な集積回路構成を行う。これらの技術により、ゲートレベルでの  $300 \mathrm{GHz}$  動作周波数の実現を目指す。また、これらの技術に基づく単一磁束量子回路を用いたストカスティック論理によるニューロ演算回路の提案・設計・集積化を行い、システムレベルで  $100 \mathrm{GHz}$  動作ニューロチップを最終目標として研究を行う。

#### Abstract

We are developing a neurochip using superconducting circuits based on a single flux-quantum logic. The circuits are fabricated by a Nb/AlOx/Nb Josephson junction process which includes high critical current density junctions, the high–speed signal propagation using microstrip lines, and multilayer interconnections. We are proposing single flux-quantum neural circuits with stochastic logic. Proposed circuits are designed and fabricated by a superconducting niobium circuit technology. This research aims at developing a neurochip with the operation frequency of 100GHz.

# 1. まえがき

超伝導体の単一磁束量子を情報担体とする回路(以下、 SFQ 回路: Single Flux-Quantum 回路) は、100GHz を 超える動作周波数で動作する最も有望な回路である。現在 の半導体回路の高速化を押し進めた場合、30GHz の動作 周波数においてチップ表面の熱放出がロケットのジェッ トノズルと同程度の発熱量になると試算されており、半導 体回路にとって代わり得る高速・低消費電力回路として最 も大規模な回路が実現されているのが SFQ 回路である。 一方、パターン認識、最適値問題、連想記憶処理など、従 来のフォンノイマン型コンピュータが苦手とする処理を 実現するシステムとしてニューラルネットワークシステ ムが期待されている。実時間で動作可能なハードウェアニ ューラルネットワークを実現する回路として、素子数の少 ない回路でシステムを実現できるストカスティック論理 に基づく回路を利用し、SFQ デバイスの高速・低消費電 力性を生かすことは有望な手法である。本研究では単一磁 束量子デバイスによるストカスティック論理に基づくニ ューロチップの開発を目指し研究を行った。

## 2. 研究内容及び成果

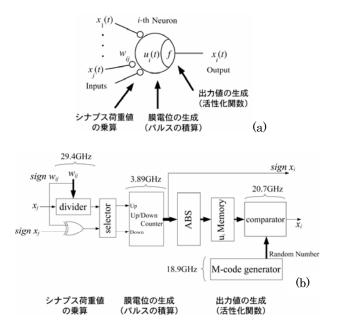

本研究ではまず SFQ 論理回路を用いたストカスティック論理ニューロ演算回路の基本構成演算ブロックの数値解析・設計を行った。図 1 にニューロン回路を実現するシステムの構成を示す。ニューロ回路の基本演算ブロックとして、入力とシナプス荷重値の乗算を行う回路、その結果を積算しニューロンの膜電位を生成する回路、膜電位の値に応じた出力を生成する活性化関数の回路が必要である。これらの演算ブロックは図 1(b)に示すように、SFQ デバイ

スを利用した基本的なディジタル演算ブロックで実現可能である。これらの演算ブロックの回路設計を 8-bit 精度で行い、その基本動作を数値シミュレーションにより明らかにした。これらの演算ブロックを接続したストカスティ

図1 ストカスティック論理ニューロシステム (a)ニューロンの工学的モデル、(b)SFQ 論理回路を用いた ストカスティック論理ニューロシステムの構成

ックニューロ演算システムは 3400 個のジョセフソン接合で実現可能であることが見積もられた。回路スピードは 16-bitのアップダウンカウンタの速度により制限され、通常のジョセフソン接合臨界電流値(2.5kA/cm²)においては 3.89GHzであると見積もられた。

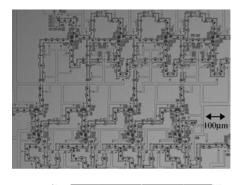

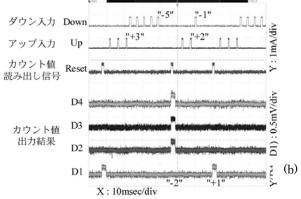

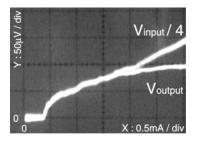

これらのシステムの集積化を目指し、Nb/AlOx/Nb接合 集積化技術を利用した回路の試作を行った。独自の集積化 プロセスでは接合のサイズが 1μ m角以下の高臨界電流密 度接合を利用した回路の集積化を行ったが、高品質の接合 特性を得ることが困難であったため、超電導工学研究所 Nb/AlOx/Nbジョセフソン接合プロセス (臨界電流値 2.5kA/cm²) を利用した回路の試作を試みた。図2に集積 化した 4 ビットアップダウンカウンタの写真と計測結果 を示す。図 1(b)に示すように、シナプス荷重値の乗算や活 性化関数ブロックは 18GHz以上の動作周波数で動作可能 である事が見込まれているが、膜電位の生成に用いるアッ プダウンカウンタは他の演算ブロックより遅く問題とな っていた。この欠点を解決するため、アップとダウンのカ ウントをそれぞれ独立のカウンタで実行し、2つのカウン ト値の差分を取る高速なアップダウンカウンタを提案し た。図 2(b)は論理動作テストの結果であり正常な論理動作 が得られている。本結果は論理動作確認のための低速での 結果であるが、高速なSFQパルス (psecオーダー) は図中 のパルスの立ち上がり時に生成・検出されている。また、 集積化したアップダウンカウンタの高速性能の評価を目 的として、ジョセフソン平均電圧法によるSFQパルス列入 力に対するカウンタ回路の出力応答の測定を行った。ジョ セフソン平均電圧法は、ジョセフソン接合に発生する直流 電圧値が磁束量子の通過する周波数に比例するという関 係式、 $V = \Phi_0 f$ 、( $\Phi_0 = 2.07 \times 10^{15}$ Wbは磁束量子、fは周 波数)に基づき、入力に直流電流を注入することでSFQパ ルス列を発生させたときの入出力に発生する電圧を計測 する方法である。図 2(c)は 2 ビットのテスト回路の計測結 果であり、4個の入力SFQパルスに対して1個の桁上げ出 力が得られることとなる。図の横軸は入力に注入する直流 電流値を表している。電流値を増加させるに従ってVinput が増加し、それに追従してVoutputが生成される。図中の入 力電圧は増幅器のレンジを調整することでVinput/4 を表示 していることから、2本の輝線が一致する電圧値まで回路 が正常に追従していることとなる。これらの結果から、2 本の電圧軌跡は  $75\mu V$  まで一致しており、これは 36GHzの出力SFQパルス(144GHz 入力SFQパルス)に相当す る。入力信号積算フェーズにおける本カウンタ回路の最大 動作周波数はビット長に依存しないため、100 GHz以上の SFQパルスをカウントする性能を持つことが本計測によ り明らかとなった。

#### 3. むすび

単一磁束量子デバイスによるストカスティック論理に基づくニューロチップの開発を目指し研究を行った。SFQ 論理回路によるニューロ演算回路の基本演算ブロックの数値解析・設計を 8-bit の精度で行い、その基本動作を数値シミュレーションにより明らかにした。演算システムは3400個のジョセフソン接合で実現可能であることが見積もられた。システム構成上律速となっていた膜電位生成用アップダウンカウンタの高速化の手法を提案し、Nb 集積プロセスによる演算ブロックの論理動作を実現した。ジョセフソン平均電圧法による同カウンタの動作を観測した結果、144GHz の入力信号に応答することが確認された。これらの結果から、ストカスティック論理ニューロ演算の実現に対して 18GHz でのシステム動作が期待される。

(a)

(c)

図2 ニューロン膜電位生成用アップダウンカウンタ(a) Nb/AlOx/Nb 接合集積回路による4ビットアップダウンカウンタ、(b)論理動作結果、(c)ジョセフソン平均電圧法による SFQ パルス列入力に対する回路の出力応答

## 【誌上発表リスト】

- [1] T. Kondo, M. Kobori, T. Onomi, and K. Nakajima, "Design and Implementation of Stochastic Neurosystem Using SFQ Logic Circuits," IEEE Trans. Applied Superconductivity, Vol.15, No.2, pp320-323 (2005 年 6 月)

- [2] T. Onomi, T. Kondo, and K. Nakajima, "High-speed single flux-quantum up/down counter for neural computation using stochastic logic," Abstracts of 8<sup>th</sup> European Conference on Applied Superconductivity, p.s5-034(2007年9月17日)

- [3] T. Onomi, T. Kondo, and K. Nakajima, "High-speed single flux-quantum up/down counter for neural computation using stochastic logic," Journal of Physics: Conference Series, Vol.97 p.012187(2008年3月19日)

#### 【報道発表リスト】

[1] "半導体進化論 イノベーター列伝 「東北大、超電 導で挑む」"、日経産業新聞、2007年6月22日